Les derniers contenus liés au tag Common Platform

GlobalFoundries : 12nm, 7nm et EUV

Nos confrères d'Anandtech ont publié une (longue) interview de Gary Patton , l'actuel CTO de GlobalFoundries. Son nom vous est peut être familier dans un autre contexte, il était auparavant en charge du R&D semiconducteurs chez IBM et plus globalement de l'alliance "Common Platform" qui liait IBM, GlobalFoundries et Samsung.

L'alliance n'est plus, l'activité semi d'IBM a été repris par GlobalFoundries (avec la transition des équipes techniques) et si GlobalFoundries et Samsung ont "partagé" le 14nm, c'est avant tout parce que GlobalFoundries avait raté son développement interne et adopté sous licence le process de Samsung. Comme nous avions eu l'occasion de vous l'indiquer, ce partenariat n'a pas duré, les relations entre GlobalFoundries et Samsung ayant été excessivement mauvaises.

En récupérant l'activité d'IBM, GlobalFoundries a récupéré un process 7nm en cours de développement et c'est celui ci qui sera utilisé par la société (voir cet article d'une interview précédente). Sur ce point, Gary Patton a confirmé les détails donnés précédemment, à savoir une version optique avant l'introduction en cours de node de l'EUV sur certaines couches (la méthode adoptée également par TSMC).

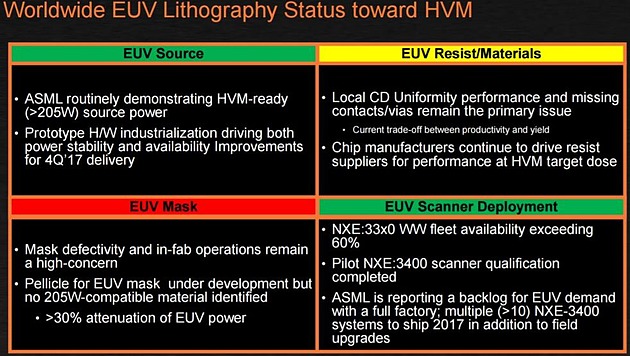

Pour l'EUV Gary Patton dit d'ailleurs ne plus avoir de doutes : le taux de disponibilité des machines serait aujourd'hui à 75% (avec pour objectif d'atteindre 85%) et la source lumineuse 250W semble être prête également côté ASML. La question du pelliculage des masques reste le gros frein même si des progrès ont été notés.

Dans ce slide de l'été dernier de Gary Patton, le pelliculage créait une atténuation de plus de 30% de la source lumineuse, et uniquement avec des sources lumineuses de moins de 205W. Aujourd'hui des matériaux semblent avoir été trouvés pour tenir 250W, et l'atténuation ne serait "que" de 20% ce qui est un net progrès.

La première version du 7nm (sans EUV) est toujours prévue en production volume vers la fin de l'année "ou plus probablement début 2019" ce qui semble être raccord avec ce que l'on a pu entendre jusqu'à présent.

A propos du 12nm qui va être utilisé par les Ryzen+, on sera surpris de voir Gary Patton indiquer que cette variante de 14nm n'est pas encore considérée en production "volume", mais que la production est pour le premier trimestre (les Ryzen+ sont attendus dès la mi-avril sur ce process). L'interview confirme des modifications principalement sur le passage 9T vers 7.5T et des améliorations sur le BEOL par rapport au 14nm.

L'interview dont l'on vous recommande la lecture balaye de nombreux autres sujets. On appréciera particulièrement la candeur du CTO en début d'interview sur les problèmes d'exécution de GF les année passées, si l'on lit entre les lignes il semble que le retard sur le 7nm soit assez léger (l'année dernière, GF avait indiqué s'attendre a voir des produits courant 2018 ce qui nous avait paru optimiste) et cohérent avec l'annonce d'un "Vega 7nm" vers la toute fin d'année.

16nm en 2013, 10nm EUV en 2015 chez TSMC

Nos confrères d'EE Times ont publié le résumé d'une présentation par TSMC de ses nodes à venir, un article dans lequel on peut relever quelques informations intéressantes.

TSMC revient d'abord rapidement sur l'état de son node 28nm. Sa Gigafab 15 produirait aujourd'hui 50000 wafers dans ce node par mois. Cette quantité devrait cependant rapidement doubler avec la mise en route de la seconde tranche de la Gigafab 15. La production devrait démarrer d'ici un mois et arriver, d'ici cinq mois, à un débit de production identique à la première tranche.

En ce qui concerne le 20nm, TSMC donne quelques détails intéressants. Avec l'arrivée du double patterning sur ce node, les gains habituels de densité et de performances devraient être réduits, une tendance que l'on avait déjà entendue du côté de la Common Platform. Le 20nm sera vraisemblablement un node de transition vers le FinFET (le node suivant en 16nm), même si TSMC se refuse de le dire. Côté performances, quelques chiffres ont été donnés à savoir 20% de fréquence en plus, ou 30% de consommation en moins par rapport au 28nm, ce qui reste tout de même assez élevé. Une vingtaine de tapeouts sont attendus cette année dans les Gigafab 12 et 14 avec une production en volume pour 2014. Parmi ceux-ci, un Cortex-A15 20nm est attendu pour le mois de mai.

Pour le 16nm, le développement du node est actuellement en cours en parallèle, on se souvient de cette annonce en début de mois d'un premier tapeout de Cortex-A57. Assez peu de détails sont donnés, si ce n'est que les premiers wafers de tests clients pourraient être lancés vers la fin de l'année avec une production qui monterait (probablement très doucement) en volume en 2014. Actuellement, TSMC travaille principalement sur des structures SRAM 128 Mbit dont les yields sont en avance par rapport aux estimations. Si les blocs logiques ont déjà été testés (cf l'annonce du Cortex), les blocs d'interface (mémoire ou autre) devraient commencer à être testés en juin.

De manière beaucoup plus surprenante, TSMC à indiquer espérer produire d'ici 2015 des wafers 10nm utilisant la technologie EUV. Pour rappel, TSMC a investit également dans le fournisseur d'outils ASML.

Une machine EUV ASML

La firme se réserve cependant assez prudente, indiquant qu'elle ne dispose toujours pas du dernier modèle d'outil de ASML (le NXE:3300 ). TSMC indique également continuer a travailler sur une technologie alternative pour ce node, le multiple electron beams sur lequel TSMC avait annoncé travailler avec MAPPER . La particularité de la technologie est qu'il ne s'agit plus littéralement de photolithographie, le masque disparaît et la source lumineuse est remplacée par des flux d'électrons qui viennent réagir avec un film préalablement déposé sur le wafer. Le débit de ces machines est qualifié par TSMC "d'encore trop lent", même s'il n'est pas comparé à celui, lui aussi très lent, de la technologie EUV actuellement (nous vous renvoyons a cette interview ou Mark Bohr évoquait le problème).

On notera enfin quelques informations sur les technologies de die stacking et les progrès en matière de 2.5D et 3D. Le concept du die stacking consiste à relier plusieurs dies directement entre eux par une couche de silicium, sans nécessiter de fils (des TSVs, Through Silicon Vias, sont utilisésà la place, ce qui permet d'augmenter significativement la bande passante et réduire la complexité). Les technologies dont on parle visent à terme à relier plusieurs dies logiques entre eux même si ce n'est pour l'instant qu'un objectif lointain.

La technologie 2.5D consiste à placer côte a côte deux dies, qui reposent sur un interposer qui contient lui-même des TSV pour interconnecter les dies. L'épaisseur de cet interposer est actuellement de 100nm mais devrait se réduire de moitié. Xilink propose actuellement un FPGA fabriqué sur le process 28HPL de TSMC qui interconnecte quatre dies, le Virtex 7 2000T.

Sur cette photo de nos confrères de 52solution , vous pouvez voir à gauche les quatre dies logiques et l'interposer. La puce assemblée est en quatrième position.

TSMC indique que les yields obtenus dépassent les 95% sur les interposers utilisés pour cette puce et plusieurs autres tape-outs devraient avoir lieu cette année, sans plus de précision. TSMC continue de travailler sur le sujet de Wide I/O avec des puces de test qui lient un die 40nm avec une puce mémoire Hynix, un montage qui a passé les tests de validation du JEDEC.

En ce qui concerne la superposition de dies (la "vraie" 3D), TSMC pense effectuer le tapeout d'une puce 28nm avec sur chaque couche des dies mémoire, avant de passer au mélange logique/mémoire. Il faudrait cependant attendre 2015 ou 2016 pour retrouver ces puces en production selon TSMC.

Notons enfin qu'en ce qui concerne le 450mm (la taille des wafers, elle est actuellement de 300mm de diamètre pour les nodes haut volume de TSMC), la production ne devrait pas démarrer au mieux avant 2016 voir 2017 malgré des tests en cours. Les outils EUV sont ceux qui poseront - là encore- le plus de problème selon TSMC, ils pourraient ne pas arriver avant 2017 en version 450mm.

Un ARM Cortex-A57 16nm chez TSMC

TSMC vient de publier un communiqué de presse indiquant le premier tape-out d'un design d'ARM Cortex-A57. Pour rappel, le Cortex-A57 est le futur SoC d'ARM basé sur l'architecture ARMv8 et qui supportera pour la première fois le 64 bits. Nous avions détaillés ici l'annonce en octobre dernier par ARM de ces architectures, indiquant que la société proposait à ses partenaires des designs pour les process 20nm, des puces prévues pour 2014 pour rappel.

On se souvient cependant qu'ARM et TSMC avaient indiqués vouloir travailler sur l'après 20nm dès l'été dernier, et c'est dans ce cadre qu'il faut lire l'arrivée de ce tape-out (une puce qui sort de la chaine de fabrication, rien ne dit qu'elle est pleinement fonctionnelle) sur le process 16nm FinFET de TSMC qui est encore en cours de mise au point. Le fabricant taïwanais indique que le portage du design d'ARM vers son process 16nm a été réalisé en moins de six mois. En octobre dernier, TSMC avait effectivement indiqué (voir ici chez nos confrères de EE Times) qu'il utiliserait un ARMv8 comme puce de test pour la mise au point de son process 16nm.

Bien entendu, si ce portage et ce premier tape-out sont intéressants, il ne dit pas grand-chose sur l'état réel d'avancement du 16nm chez TSMC, ni même du 20nm. Pour rappel, TSMC utilisera pour le 20nm un design planaire basé sur un double patterning, à l'image de GlobalFoundries et des membres de la Common Platform. Et tout comme GlobalFoundries, TSMC semble vouloir accélérer la cadence pour passer le plus vite possible à la génération suivante (16nm chez TSMC, 14 chez GloFo) qui utiliseront les FinFET. Le 20nm devrait décidément avoir une durée de vie assez courte chez la plupart des constructeurs

Focus : Common Platform Technology Forum 2013

Les acteurs de la Common Platform Alliance tenaient hier leur conférence technologique annuelle, le Common Platform Technology Forum. Pour cette sixième édition (voir notre couverture de l'édition précédente), IBM, GlobalFoundries et Samsung ont tenu a présenter quelques unes des grandes orientations technologiques pour les années a venir. Signe des temps, ARM était partenaire privilégié de la conférence et a également effectué une présentation sur laquelle nous reviendrons un peu plus...

[+] Lire la suite

Common Platform Technology Forum 2012

IBM, GlobalFoundries et Samsung tenaient aujourd'hui leur Technology Forum. Les trois sociétés travaillent pour rappel en commun sur le développement de leurs procédés de fabrications. Sans s'avancer réellement dans des annonces précises, les différentes sessions nous ont permis de noter quelques points intéressants.

D'abord, comme nous l'évoquions la semaine dernière, le 28nm développé par GlobalFoundries et ses autres partenaires fait l'impasse sur le SOI de type "partially-depleted" (PD-SOI), difficile à porter efficacement lorsque la finesse de gravure progresse, ce qui rend l'attrait de la technologie limitée. Si le PD-SOI est bel et bien mis au rebus (il a été confirmé qu'il ne refera pas son apparition sur le 20nm), cela ne signifie cependant pas l'arrêt total du SOI. Pour le 20nm et suivant, l'avenir selon le Dr Gary Patton d'IBM est au ETSOI. Il s'agit d'un type Fully Depleted, c'est-à-dire que le corps du transistor en lui-même qui aplani afin de contrer les effets du SOI classique. Si IBM aura mentionné plusieurs fois la présence de l'ETSOI, on notera que ce n'était pas le cas de ses partenaires qui ne se sont pas engagés précisément sur le sujet. L'allongement du délai de développement ainsi que le surcoût direct engendré sur les wafers peut en effet pousser les différents acteurs de la Common Platform à proposer, par exemple, un process avec ETSOI et un sans pour satisfaire la demande des clients. IBM aura confirmé au passage que l'ETSOI a été développé pour le 20nm en collaboration avec ST Micro.

En ce qui concerne le 20nm, une annonce à tout de même été faite, celle de la nécessité du double patterning. La technologie consiste à utiliser deux expositions successives avec des masques différents pour réaliser une même couche métallique. Si toutes les couches ne sont pas concernées par la nécessité du double patterning, l'ajout des masques crée un surcoût notable. On aura noté d'ailleurs ce slide relativement édifiant sur les couts du 32/28 et du 22/20 nm :

Le surcoût sur les masques est particulièrement élevé tout comme le coût des outils de design (EDA) et du design en lui-même qui explosent en partie à cause de la complexification due au double patterning. Intel devrait lui aussi faire appel à de telles techniques pour le 16nm, cependant à notre connaissance ce n'est pas le cas pour le 22.

Autre annonce ferme, mais presque connue, l'arrivée des transistors FinFET. Pour rappel, Intel a décidé, dès le 22nm (qui arrivera sous peu avec les processeurs Ivy Bridge) de modifier la forme des transistors qui ne sont plus construits sur un plan, mais dans l'espace (voir notre focus sur le sujet pour plus de détails). Les membres de la Common Platform ont confirmé qu'il arriverait pour le 16nm, ce qui avait été sous entendu précédemment.

Le doublement de la densité à chaque node s'accompagne de gains de performances annoncés à 1.6x

En ce qui concerne l'au-delà du 10nm, considéré comme une barrière technologique pour les méthodes actuelles, IBM a évoqué plusieurs pistes comme l'utilisation de nanotubes de carbone. De ce côté, IBM a annoncé avoir développé de nouvelles méthodes pour trier plus facilement les nanotubes utilisables de ceux qui ne le sont pas. Gary Patton évoquait ainsi que 30% des nanotubes semi conducteurs produits étaient pleinement conducteurs et devaient donc être supprimés. En ce qui concerne la lithographie EUV, qui se fait attendre depuis plusieurs générations, il faudra encore attendre. Si IBM laissait entre ouverte une porte pour le 16nm, il est plus probable que la technologie ne soit pas à l'heure pour ce node.

Nous aurons noté enfin durant la conférence quelques petites phrases. D'abord, et à plusieurs reprises, des allusions sur le fait que les fabs 28nm de la Common Platform étaient fonctionnelles et non pas arrêtées. Un écho à un article relativement surprenant publié par nos confrères de SemiAccurate la semaine dernière qui indiquait que TSMC aurait stoppé complètement la production sur ses lignes 28nm il y a trois semaines de cela, pour un problème qui n'aurait pas été précisé. Une information difficile à vérifier et si nous avions entendu un temps des rumeurs sur d'éventuels retards de livraisons pour certains GPU produits par TSMC, elles se sont estompées depuis. La référence - multiple - à cette rumeur par les concurrents de TSMC était pour le moins originale.

On aura noté enfin, de la part de Subramani Kengeri de GlobalFoundries que si jusqu'ici la production de CPU et de GPU avait poussé en avant le développement des process de technologies, c'est aujourd'hui les SoC et les puces basse consommation qui forcent les décisions de design. AMD appréciera.