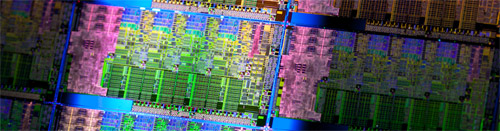

Intel Core i7 et Core i5 LGA 1155 Sandy Bridge

Les améliorations du core Sandy BridgeSandy Bridge repose principalement sur l'architecture Nehalem, mais apporte son lot d'améliorations, dont certaines sont reprises de la micro-architecture Netburst du Pentium 4. Netburst a eu cela de bénéfique de ne pas reposer sur une architecture existante, et son étude a ainsi pu déboucher sur une multitude de concepts inédits dans le monde du x86. L'Hyper-Threading réapparu avec Nehalem est l'une d'elles, et la micro-architecture Sandy Bridge remet également au goût du jour certaines "innovations" de Netburst.

Un cache "L0"Lors de notre étude de l'architecture Nehalem, nous avons vu que ce processeur inclut un mécanisme de gestion optimisé des boucles qui repose sur un buffer contenant les micro-opérations (c'est-à-dire les instructions déjà décodées), évitant ainsi de décoder plusieurs fois le même code d'une boucle lorsque celle-ci est correctement prédite. Nous avions d'ailleurs évoqué la ressemblance avec le principe du trace cache du Pentium 4.

Sandy Bridge va un cran plus loin en introduisant un cache de micro-opérations (uop cache) de 1,5 Ko, recevant ses données des unités de décodage des instructions. L'unité de branchement y accède dès lors qu'une nouvelle branche est prédite et en cas de succès, la majeure partie du traitement "front end" (de la récupération des instructions au décodage) devient inutile. Cela résulte en une utilisation moindre des unités du front end, et au final une amélioration sensible du niveau de performance par watt consommé. A noter que le uop cache du Sandy Bridge n'est pas véritablement comparable au trace cache du Pentium 4 : en effet le Sandy Bridge conserve son cache L1 dédié aux instructions et les deux caches fonctionnent de concert ; au contraire du Pentium 4 dont le trace cache se substituait intégralement au L1I et était donc d'un fonctionnement plus complexe.

Une gestion des registres inspirée du Pentium 4Pour Sandy Bridge, les ingénieurs d'Intel ont choisi d'utiliser un fichier de registres physiques (PRF ou Physical Register File) comme c'était le cas sur le Pentium 4. Pour comprendre en quoi cela consiste exactement et les motivations de ce choix, il faut rappeler quelques concepts inhérents à la gestion des registres par un processeur x86.

Les processeurs x86 se caractérisent par un faible nombre de registres : 8 en mode 32-bits, et 16 en mode 64-bits (à titre de comparaison, un processeur IA64 comme l'Itanium en possède 128). Ce sont les fameux registres eax, ebx, familiers pour qui a déjà vu du code assembleur x86, et qui constituent le fichier de registres (register file en anglais).

Or, les processeurs modernes utilisent des moteurs d'exécution out-of-order (OOO), c'est-à-dire capables de traiter les instructions dans un ordre différent de celui du code assembleur écrit par le programmeur ou généré par un compilateur. Afin de faciliter le travail de l'OOO, les processeurs possèdent en interne bien plus de 8 registres, et ont donc recours au renommage de registres (register renaming) pour maintenir la cohérence entre les registres physiques du processeur (internes, et non visibles par les programmeurs), et les registres architecturaux (ceux exploitables par le programmeur : eax, ebx ) auxquels ils font référence.

En pratique, le processeur a recours à un buffer de réordonnancement des instructions, appelé Reorder Buffer ou ROB, dont la fonction est de restaurer l'ordre des instructions telles qu'elles apparaissent dans le programme après que celles-ci aient été exécutées, éventuellement dans un ordre différent. Sur les architectures dérivées du P6 (Core 2, Nehalem et Westmere), le ROB contient les résultats de chaque micro-opération en cours, accompagné d'un index de registre permettant de rétablir la correspondance entre les registres physiques et les registres architecturaux. Au final, ces résultats sont copiés vers un fichier de registres de retrait, ou Retirement Register File (RRF), qui correspond à l'ensemble des registres architecturaux après le traitement.

En son temps, l'architecture Netburst a modifié ce schéma par l'utilisation d'un fichier contenant les registres physiques (internes) du processeur (Physical Register File, ou PRF). Le ROB ne contient alors plus les données des micro-opérations en cours, mais uniquement une référence vers ce fichier de registres. L'intérêt est évident : chaque entrée du ROB occupe moins de place, et à capacité égale, le ROB peut donc contenir plus d'entrées (le ROB de Sandy Bridge en contient 168, et celui de Nehalem / Westmere 128). Le RRF n'existe plus, et la cohérence avec les registres architecturaux passe par une table appelée Register Alias Table (RAT), dont les entrées pointent également vers le PRF. Ces références vers le PRF évitent ainsi les phases de copies de données que l'on rencontre dans le schéma ROB + RRF, qui est d'autant plus pénalisante que ces données sont larges.

L'utilisation d'un PRF sur le Pentium 4 a ainsi été motivée par l'optimisation de Netburst pour les jeux d'instructions tels que SSE et SSE2, qui manipulent des données de 128 bits. Sandy Bridge inaugure quant à lui le nouveau jeu d'instructions AVX dont les opérandes peuvent atteindre 256 bits, ce qui a poussé Intel à équiper sa nouvelle architecture d'un PRF également.

Sommaire

1 - L'architecture Sandy Bridge

2 - Les améliorations du core

3 - Les améliorations du core, suite

4 - Advanced Vector Extension (AVX)

5 - Turbo Boost version 2

6 - Socket LGA 1155, P67 et H67, LGA 2011

7 - Les Core i7 & i5 Sandy Bridge

8 - Intel HD Graphics 2000 & 3000

9 - Intel HD Graphics, conso, oc, perfs

10 - Intel HD Graphics, CPU vs IGP

11 - Intel HD Graphics, Vidéo et Quick Sync

12 - Consommation

2 - Les améliorations du core

3 - Les améliorations du core, suite

4 - Advanced Vector Extension (AVX)

5 - Turbo Boost version 2

6 - Socket LGA 1155, P67 et H67, LGA 2011

7 - Les Core i7 & i5 Sandy Bridge

8 - Intel HD Graphics 2000 & 3000

9 - Intel HD Graphics, conso, oc, perfs

10 - Intel HD Graphics, CPU vs IGP

11 - Intel HD Graphics, Vidéo et Quick Sync

12 - Consommation

Vos réactions

Contenus relatifs

- [+] 09/05: AMD Ryzen 7 2700, Ryzen 5 2600 et I...

- [+] 05/04: Pas de MAJ Microcode pour les Gulft...

- [+] 03/04: Intel lance la 2ème vague de sa 8èm...

- [+] 05/10: Intel Core i7-8700K, Core i5-8600K,...

- [+] 12/09: Core i7-7820X : Un Skylake-X mieux ...

- [+] 07/09: Les Skylake en fin de vie chez Inte...

- [+] 23/08: Coffee Lake incompatible avec les L...

- [+] 29/06: Intel Core i9-7900X et Core i7-7740...

- [+] 03/01: Core i5-7600K et i7-7700K : pour qu...

- [+] 28/12: Gigabyte BRIX Gaming GT